# SWITCHING THEORY AND LOGIC DESIGN COURSEFILE

## **Coursefile contents:**

- 1. Cover Page

- 2. Syllabus copy

- 3. Vision of the department

- 4. Mission of the department

- 5. PEOs and POs

- 6. Course objectives and outcomes

- 7. Brief note on the importance of the course and how it fits in to the curriculum

- 8. Prerequisites

- 9. Instructional Learning Outcomes

- 10. Course mapping with PEOs and POs

- 11. Class Time Table

- 12. Individual Time Table

- $13. Lecture \ schedule \ with \ methodology \ being \ used/adopted$

- 14. Detailed notes

- 15. Additional/missing topics

- 16. University previous Question papers

- 17. Question Bank

- 18. Assignment topics

- 19. Unit wise questions

- 20. Tutorial problems

- 21. Known gaps

- 22. Discussion topics

- 23. References, Journals, websites and E-links

- 24. Quality measurement Sheets

- a. course and survey

- b. Teaching evaluation

- 25. Student List

- 26. GroupWise Student List for discussion topics

#### GEETHANJALI COLLEGE OF ENGINEERING AND TECHNOLOGY

#### **DEPARTMENT OF** Electrical and Electronics Engineering

(Name of the Subject / Lab Course): Switching Theory and Logic Design

(JNTU CODE –A40407) Programme: UG

Branch: Electrical and Electronics Engineering Version No : 01

Year: II year Generated on: 05/11/15

Semester: *II-Sem* No. of pages:

Classification status (<u>Unrestricted</u> / Restricted )

**Distribution List:**

Prepared by: 1) Name: D.Radhika, 1) Name:

2) Sign : 2) Sign :

3) Design: Assoc. Prof 3) Design:

4) Date : 05/11/2015 4) Date :

Verified by: 1) Name : \* For Q.C Only.

2) Sign : 1) Name :

3) Design: 2) Sign:

4) Date : 3) Design :

4) **Date** :

Approved by : (HOD ) 1) Name :

2) Sign :

3) Date :

## 2. Syllabus copy

#### JAWAHARLAL NEHRU TECHNOLOGIVAL UNIVERSITY HYDERABAD

II Year B.Tech. EEE -II Sem

L T/P/D C

#### SWITCHING THEORY AND LOGIC DESIGN

#### **UNIT I**

#### NUMBER SYSTEMS AND BOOLEAN ALGEBRA AND SWITCHING FUNCTIONS: Number

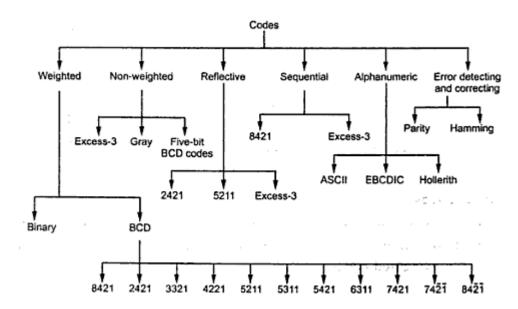

**systems**: Base Conversion Methods, Complement of Numbers, Codes - Binary codes, Binary Coded Decimal code and its properties, Unit distance codes, Alpha Numeric codes, Error detecting and correcting codes.

Boolean Algebra: Basic theorems and properties

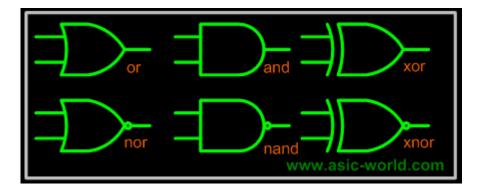

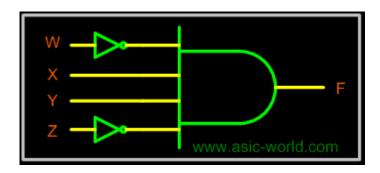

Switching Functions: Canonical and Standard forms, Algebraic simplification of digital logic gates,

Properties of XOR gates, Universal gates, Multilevel NAND/NOR realizations.

#### **UNIT II**

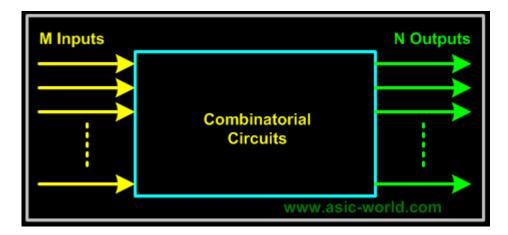

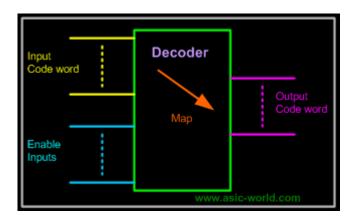

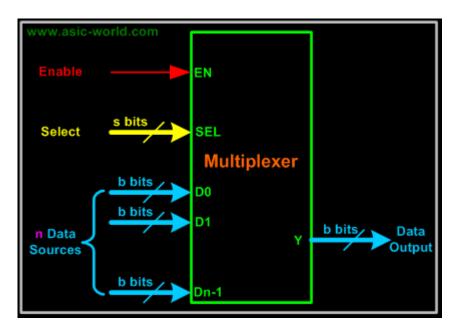

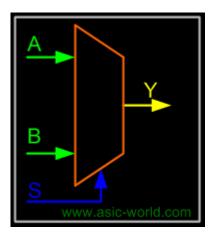

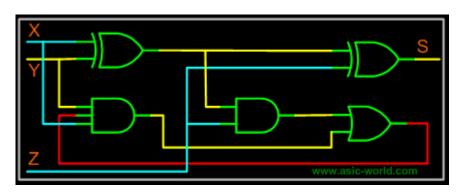

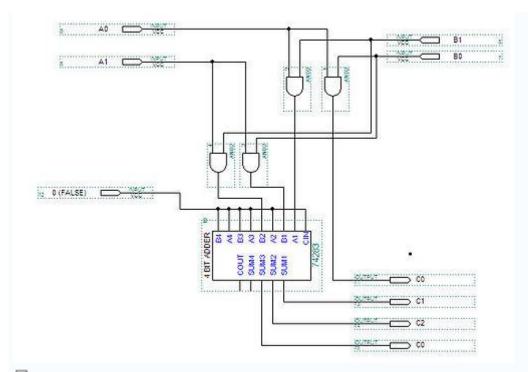

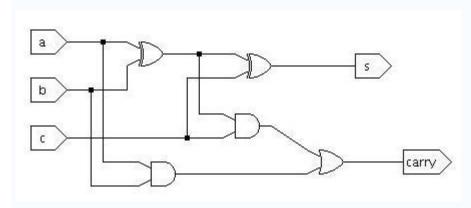

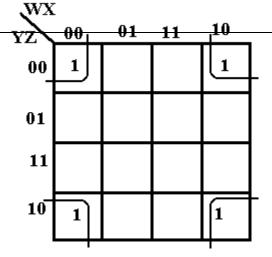

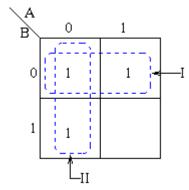

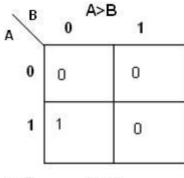

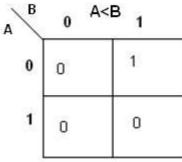

MINIMIZATION AND DEGIN OF COMBINATIONAL CIRCUITS: Introduction, The Minimization with theorem, The Karnaugh Map Method, Five and Six variable Maps, Prime and Essential Implications, Don't care Map entries, Using the maps for Simplifying, Tabular method, Partially specified Expressions, Multi-Output Minimization, Minimization and combinational Design, Arithmetic Circuits, Comparator, Multiplexers, Code Converters, Wired Logic, Tristate Bus system, Practical Aspects related to Combinational Logic Design, Hazards and Hazard Free Relations.

#### **UNIT III**

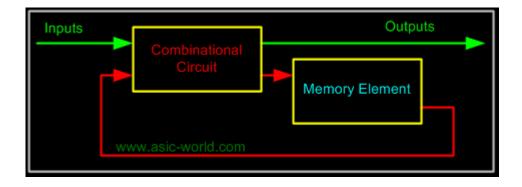

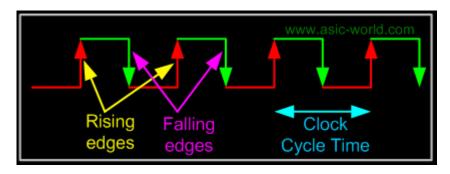

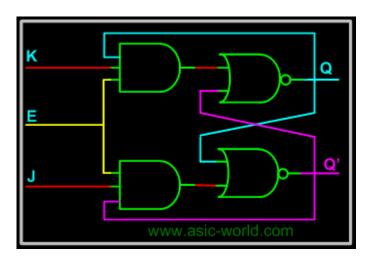

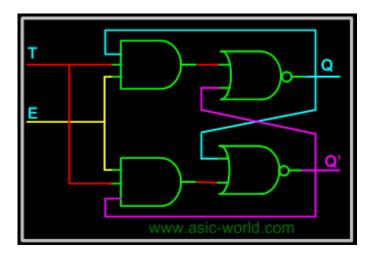

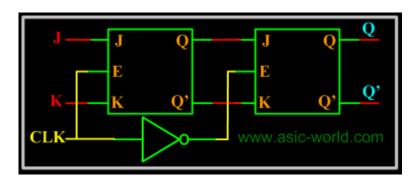

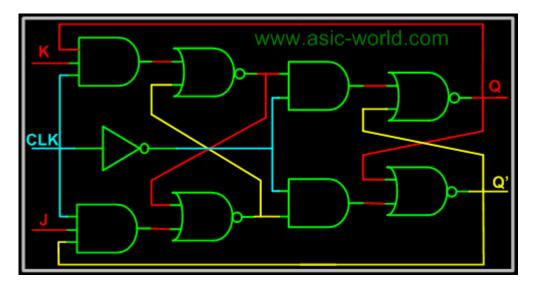

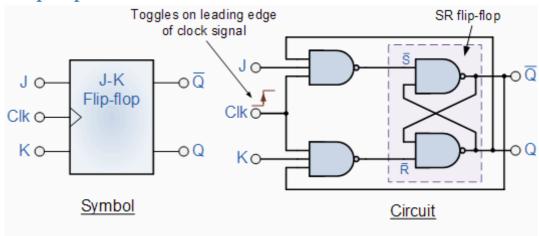

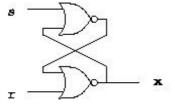

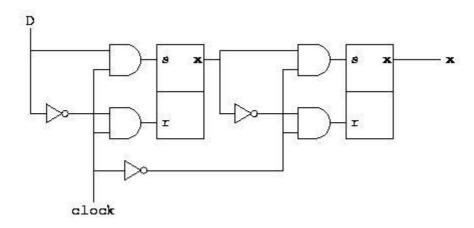

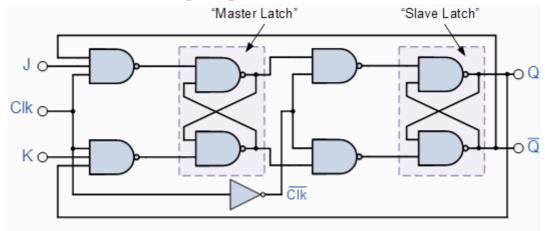

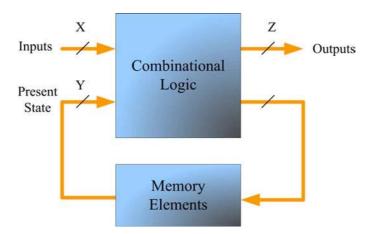

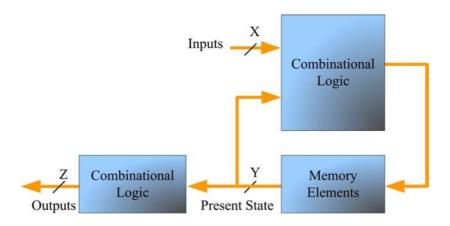

**SEQUENCTIAL MACHINES FUNDAMENTALS:** Introduction, Basic Architectural Distinctions between Combinational and Sequential circuits, the Binary Cell, Fundamentals of Sequential Machine Operation, The Flip-Flop, The D- Latch Flip-Flop, the Clocked T Flip-Flop, the clocked J-K Flip-Flop, Design of a clocked Flip-flop, conversion from one Type of Flip-Flop to another, Timing and Triggering considerations, Clock skew.

#### **UNIT IV**

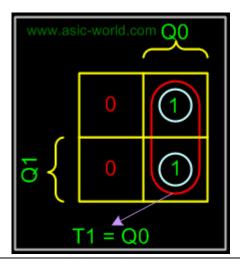

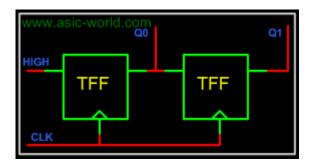

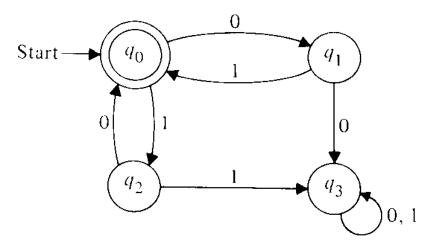

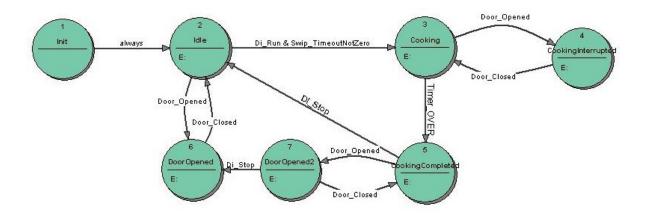

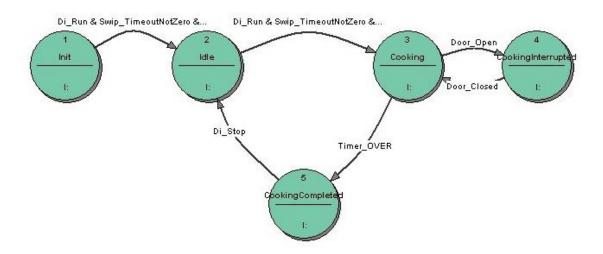

**SEQUENTIAL CIRCUITS DESIGN AND ANALYSIS:** Introduction, State diagram, Analysis of Synchronous Sequential Circuits, Approaches to the Design of Synchronous sequential Finite State Machines, Design Aspects, State Reduction, Design Steps, Realization using Flip-Flops. **Counters:** Design Of Single Mode Counters; Ripple Counter, Ring Counter, Shift Register, Shift Register Sequences, Ring Counter using Shift Register.

#### **UNIT V**

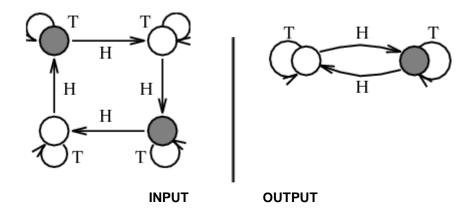

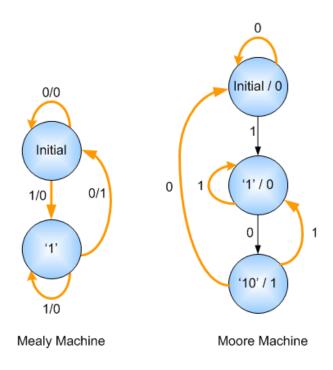

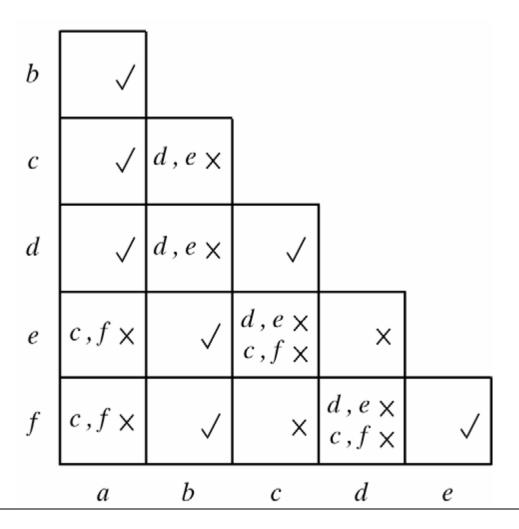

**SEQUENTIAL CIRCUITS:** Finite state machine-capabilities and limitations, Mealy and Moore models-minimization of completely specified and incompletely specified sequential machines, Partition techniques and Merger chart methods-concept of minimal cover table.

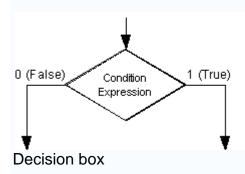

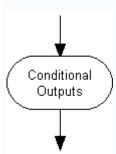

**ALGOROTHIMIC STATE MACHINES:** Salient features of the ASM chart-Simple examples-System design using data path and control subsystems-control implementations-examples of Weighing machine and Binary multiplier.

## **TEXT BOOKS:**

- 1. Switching & Finite Automata theory Zvi Kohavi and Neeraj K Jha, 3<sup>rd</sup> Edition, Cambridge.

- 2. Digital Design Morris Mano, PHI, 3rd Edition.

#### **REFERENCE BOOKS:**

- 1. Introduction to Switching Theory and Logic Design Fredriac J Hill, Gerald R Peterson,  $3^{rd}$  Edition, John Willey and Sons Inc,

- 2. Digital Fundamentals A Systems approach Thomas L Floyd, Pearson, 2013.

- 3. Digital Logic Design Ye Brian and HoldsWorth, Elsevier

- 4. Fundamentals of Logic Design Charles H. Roth, Thomson Publications, 5th Edition, 2004

- 5. Digital Logic Applications and Design John M. Yarbrough, Thomson Publications, 2006

- 6. Digital logic and state machine design Comer, 3<sup>rd</sup>, Oxford 2013.

#### 3. Vision of EEE

To provide excellent Electrical and electronics education by building strong teaching and research environment

#### 4. Mission of EEE

To offer high quality graduate program in Electrical and Electronics education and to prepare students for professional career or higher studies. The department promotes excellence in teaching, research, collaborative activities and positive contributions to society

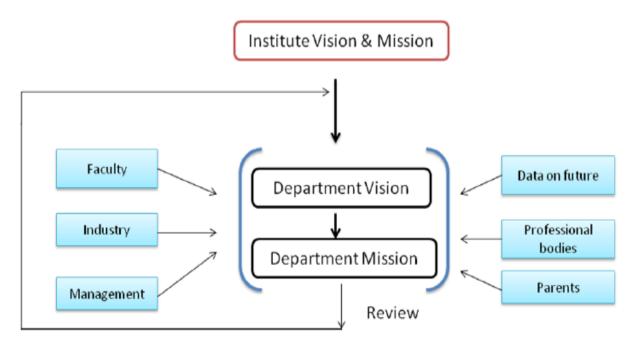

Figure 1.1: Process for defining Vision and Mission of the Department

## **5.1 PROGRAM EDUCATIONAL OBJECTIVES**

PEO 1. Graduates will excel in professional career and/or higher education by acquiring knowledge in Mathematics, Science, Engineering principles and Computational skills.

PEO 2. Graduates will analyze real life problems, design Electrical systems appropriate to the requirement that are technically sound, economically feasible and socially acceptable.

PEO 3.Graduates will exhibit professionalism, ethical attitude, communication skills, team work in their profession, adapt to current trends by engaging in lifelong learning and participate in Research & Development.

#### **5.2 PROGRAM OUTCOMES**

The Program Outcomes of UG in Electrical and Electronics Engineering are as follows

- PO 1. An ability to apply the knowledge of Mathematics, Science and Engineering in Electrical and Electronics Engineering.

- PO 2. An ability to design and conduct experiments pertaining to Electrical and Electronics Engineering.

- PO 3. An ability to function in multidisciplinary teams

- PO 4. An ability to simulate and determine the parameters such as nominal voltage current, power and associated attributes.

- PO 5. An ability to identify, formulate and solve problems in the areas of Electrical and Electronics Engineering.

- PO 6. An ability to use appropriate network theorems to solve electrical engineering problems.

- PO 7. An ability to communicate effectively.

- PO 8. An ability to visualize the impact of electrical engineering solutions in global, economic and societal context.

- PO 9. Recognition of the need and an ability to engage in life-long learning.

- PO 10 An ability to understand contemporary issues related to alternate energy sources.

- PO 11 An ability to use the techniques, skills and modern engineering tools necessary for Electrical Engineering Practice.

- PO 12 An ability to simulate and determine the parameters like voltage profile and current ratings of transmission lines in Power Systems.

- PO 13 An ability to understand and determine the performance of electrical machines namely speed, torque, efficiency etc.

- PO 14 An ability to apply electrical engineering and management principles to Power Projects.

## **6.1 COURSE OBJECTIVES**

| S.No | Objectives                                                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | To learn basic tools for the design of digital circuits and fundamental concepts used in the design of digital systems                          |

| 2    | To Understand common forms of number representation in digital electronic circuits and to be able to convert between different representations. |

| 3    | To implement simple logical operations using combinational logic circuits                                                                       |

| 4    | To design combinational logic circuits, sequential logic circuits                                                                               |

| 5    | To impart to student the concepts of sequential circuits, enabling them to analyze sequential systems in terms of state machines.               |

| 6    | To implement synchronous state machines using flip flops.                                                                                       |

#### **6.2 COURSE OUTCOMES**

| S.No. | Outcome                                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Able to manipulate numeric information in different forms, e.g. different bases, signed integers, various codes such as ASCII, gray, and BCD.                    |

| 2     | Able to manipulate simple Boolean expressions using the theorems and postulates of Boolean algebra and to minimize combinational functions.                      |

| 3     | Able to design and analyze small combinational circuits and to use standard combinational functions/building blocks to build larger more complex circuits.       |

| 4     | Able to design and analyze small sequential circuits and devices and to use standard sequential functions/building blocks to build larger more complex circuits. |

#### 7. BRIEF NOTE ON THE IMPORTANE OF THE COURSE:

- a. This Course provides in-depth knowledge of switching theory and design techniques of digital circuits, which is the basis for design of any digital circuit.

- b. This subject is required to understand the later subjects like LDICA, MPMC, VLSI& ES, etc.

- c. By studying this subject, the students can design and understand digital systems and its importance.

- d. The students logical thinking capability will be improved which will help in placements and in their future technical assignments.

## 8. PREREQUISITES:

- 1. Set theory (Mathematics)

- 2. Basic logic operations like bit wise operations, Shift operations, flow charts, ASCII codes, etc. (Computer Programming)

## 9. INSTRUCTIONAL LEARNING OUTCOMES

## UNIT-I

| Sl  | Module              | Outcomes                                               |

|-----|---------------------|--------------------------------------------------------|

| No. |                     |                                                        |

| 1   |                     | Able to Know different number systems                  |

| 2   |                     | Able to do Conversion Operations between different     |

|     | Number System and   | number systems                                         |

| 3   | Boolean Algebra and | Able to know basic theorems and properties used in     |

|     | Switching Functions | Boolean algebra                                        |

| 4   |                     | Designs different logic circuits using different logic |

|     |                     | gates                                                  |

| 5   |                     | Designs multilevel realization functions               |

## UNIT-II

| Sl  | Module                    | Outcomes                                             |

|-----|---------------------------|------------------------------------------------------|

| No. |                           |                                                      |

| 1   |                           | Able to get basic information in the design of       |

|     |                           | combinational circuits                               |

| 2   | Minimization and Design   | Able to solve and analyze Karnaugh Maps              |

| 3   | of Combinational Circuits | Designs Combinational multi level circuits           |

| 4   |                           | Able to know the operation of Multiplexers and other |

|     |                           | arithmetic circuits                                  |

| 5   |                           | Can perform practical's with combinational logic     |

|     |                           | circuits                                             |

## UNIT-III

| Sl  | Module              | Outcomes                                         |

|-----|---------------------|--------------------------------------------------|

| No. |                     |                                                  |

| 1   |                     | Able to identify architectural differences in    |

|     |                     | combinational and sequential circuits            |

| 2   | Sequential machines | Able to design sequential circuits for machine   |

|     | fundamentals        | operation                                        |

| 3   |                     | Able to design Clocked flip flops                |

| 4   |                     | Makes use of timing and triggering circuits with |

|     |                     | sequential logics                                |

## UNIT-IV

| Sl  | Module                    | Outcomes                                          |  |  |  |  |  |  |  |  |

|-----|---------------------------|---------------------------------------------------|--|--|--|--|--|--|--|--|

| No. |                           |                                                   |  |  |  |  |  |  |  |  |

| 1   |                           | Able to draw state diagrams                       |  |  |  |  |  |  |  |  |

| 2   |                           | Able to analyze synchronous sequential circuits   |  |  |  |  |  |  |  |  |

| 3   | Sequential circuit design | Designs sequential finite state machines          |  |  |  |  |  |  |  |  |

| 4   | and analysis              | Designs different types of counters and registers |  |  |  |  |  |  |  |  |

## UNIT-V

| Sl  | Module                     | Outcomes                                                |

|-----|----------------------------|---------------------------------------------------------|

| No. |                            |                                                         |

| 1   |                            | Able to identify capabilities and limitations of finite |

|     |                            | state machine                                           |

| 2   |                            | Able to know Mealy and Moore minimization               |

|     | Sequential circuits and    | models                                                  |

| 3   | algorithmic state machines | Able to know partition techniques and merger chart      |

|     |                            | methods                                                 |

| 4   |                            | Able to know about concept of minimal cover table       |

| 5   |                            | Able to design any system using data path and           |

|     |                            | controls subsystems                                     |

| 6   |                            | Knows the control logics of weighing machine and        |

|     |                            | binary multiplier                                       |

# 10. Course mapping with PEOs and POs

## **Mapping of Course with Programme Educational Objectives:**

| S.No | Course component       | code | course | Semester | PEO 1 | PEO 2     | PEO 3 |

|------|------------------------|------|--------|----------|-------|-----------|-------|

| 1    | Digital<br>Electronics |      | STLD   | II       | V     | $\sqrt{}$ |       |

## **Mapping of Course outcomes with Programme outcomes:**

\*When the course outcome weightage is < 40%, it will be given as moderately correlated (1).

\*When the course outcome weightage is >40%, it will be given as strongly correlated (2).

| POs                    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 |         |

|------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|---------|

| STLD                   | 2 | 2 | 2 | 1 | 2 |   |   |   | 1 | 1  | 2  | 2  | 2  |         |

| CO 1:                  | 2 | 2 | 2 | 1 | 2 |   |   |   | 1 | 1  | 2  | 2  | 2  |         |

| a. Explain different   |   |   |   |   |   |   |   |   |   |    |    |    |    |         |

| Number Systems,        |   |   |   |   |   |   |   |   |   |    |    |    |    | US      |

| Codes and their        |   |   |   |   |   |   |   |   |   |    |    |    |    | Systems |

| Conversions.           |   |   |   |   |   |   |   |   |   |    |    |    |    | ıl Sy   |

| b. Explain Error       |   |   |   |   |   |   |   |   |   |    |    |    |    | Digital |

| Detecting & Error      |   |   |   |   |   |   |   |   |   |    |    |    |    | D       |

| Correcting Codes       |   |   |   |   |   |   |   |   |   |    |    |    |    |         |

| c. Solve typical       |   |   |   |   |   |   |   |   |   |    |    |    |    |         |

| problems on the above. |   |   |   |   |   |   |   |   |   |    |    |    |    |         |

| CO 2:                    | 2 | 2 | 2 | 1 | 2 |  | 1 | 1 | 2 | 2 | 2 |  |

|--------------------------|---|---|---|---|---|--|---|---|---|---|---|--|

| Represent the given      |   |   |   |   |   |  |   |   |   |   |   |  |

| Boolean / Switching      |   |   |   |   |   |  |   |   |   |   |   |  |

| functions in various     |   |   |   |   |   |  |   |   |   |   |   |  |

| forms, prove Boolean     |   |   |   |   |   |  |   |   |   |   |   |  |

| Theorems, and            |   |   |   |   |   |  |   |   |   |   |   |  |

| minimize Boolean         |   |   |   |   |   |  |   |   |   |   |   |  |

| functions using these    |   |   |   |   |   |  |   |   |   |   |   |  |

| Theorems. Realize        |   |   |   |   |   |  |   |   |   |   |   |  |

| Switching functions      |   |   |   |   |   |  |   |   |   |   |   |  |

| using basic logic        |   |   |   |   |   |  |   |   |   |   |   |  |

| gates/universal gates.   |   |   |   |   |   |  |   |   |   |   |   |  |

| CO 3:                    | 2 | 2 | 2 | 1 | 2 |  | 1 | 1 | 2 | 2 | 2 |  |

| a. Minimize the given    |   |   |   |   |   |  |   |   |   |   |   |  |

| Switching functions in   |   |   |   |   |   |  |   |   |   |   |   |  |

| SoP and PoS forms        |   |   |   |   |   |  |   |   |   |   |   |  |

| using K-Map.             |   |   |   |   |   |  |   |   |   |   |   |  |

| b. Given a switching a   |   |   |   |   |   |  |   |   |   |   |   |  |

| function, generate the   |   |   |   |   |   |  |   |   |   |   |   |  |

| set of Prime Implicants  |   |   |   |   |   |  |   |   |   |   |   |  |

| using Tabular Method     |   |   |   |   |   |  |   |   |   |   |   |  |

| and minimize the         |   |   |   |   |   |  |   |   |   |   |   |  |

| function.                |   |   |   |   |   |  |   |   |   |   |   |  |

| CO 4:                    | 2 | 2 | 2 | 1 | 2 |  | 1 | 1 | 2 | 2 | 2 |  |

| Design the different     |   |   |   |   |   |  |   |   |   |   |   |  |

| types of combinational   |   |   |   |   |   |  |   |   |   |   |   |  |

| logic circuits.          |   |   |   |   |   |  |   |   |   |   |   |  |

| CO 5:                    | 2 | 2 | 2 | 1 | 2 |  | 1 | 1 | 2 | 2 | 2 |  |

| Design combinational     |   |   |   |   |   |  |   |   |   |   |   |  |

| logic circuits using     |   |   |   |   |   |  |   |   |   |   |   |  |

| different types of PLDs, |   |   |   |   |   |  |   |   |   |   |   |  |

| namely, PROM, PLA and PAL. |   |   |   |   |   |   |   |   |   |   |   |  |

|----------------------------|---|---|---|---|---|---|---|---|---|---|---|--|

| CO 6:                      | 2 | 2 | 2 | 1 | 2 |   | 1 | 1 | 2 | 2 | 2 |  |

| Design different types     |   |   |   |   |   |   |   |   |   |   |   |  |

| of synchronous             |   |   |   |   |   |   |   |   |   |   |   |  |

| sequential logic           |   |   |   |   |   |   |   |   |   |   |   |  |

| circuits.                  |   |   |   |   |   |   |   |   |   |   |   |  |

| CO 7:                      | 2 | 2 | 2 | 1 | 2 |   | 1 | 1 | 2 | 2 | 2 |  |

| Design fundamental         |   |   |   |   |   |   |   |   |   |   |   |  |

| mode and pulse mode        |   |   |   |   |   |   |   |   |   |   |   |  |

| asynchronous               |   |   |   |   |   |   |   |   |   |   |   |  |

| sequential machines.       |   |   |   |   |   |   |   |   |   |   |   |  |

| CO 8:                      | 2 | 2 |   |   | 2 | 2 | 1 | 1 | 2 | 2 | 2 |  |

| Design digital systems     |   |   |   |   |   |   |   |   |   |   |   |  |

| using ASM Charts.          |   |   |   |   |   |   |   |   |   |   |   |  |

|                              | Geethanjali College of Engineering & Technology                                        |                           |                 |                             |                 |              |                         |                                        |        |              |  |  |

|------------------------------|----------------------------------------------------------------------------------------|---------------------------|-----------------|-----------------------------|-----------------|--------------|-------------------------|----------------------------------------|--------|--------------|--|--|

|                              | Department of Electrical & Electronics Engineering                                     |                           |                 |                             |                 |              |                         |                                        |        |              |  |  |

| Year/Sem/S                   | Year/Sem/Sec: II-B. Tech-II Sem(Version-0) Room No: Acad Year 2015-16, WEF: 07-12-2015 |                           |                 |                             |                 |              |                         |                                        |        |              |  |  |

| Class Teacher: Mrs.D.Radhika |                                                                                        |                           |                 |                             |                 |              |                         |                                        |        |              |  |  |

| Time                         | 09.30-<br>10.20                                                                        | 10.20-<br>11.10           | 11.10-<br>12.00 | 12.00-12.50                 | 12.50-<br>13.30 | 13.30-14     | 13.30-14.20 14.20-15.10 |                                        |        | 15.10-16.00  |  |  |

| Period                       | 1                                                                                      | 2                         | 3               | 4                           |                 | 5            |                         | 6                                      |        | 7            |  |  |

| Monday                       | EC                                                                                     | NT                        | EM-II           | PS-I                        |                 | MEFA         |                         | CACHE/SPORTS/<br>LIBRARY/<br>MENTORING |        | ARY/         |  |  |

| Tuesday                      | STLD                                                                                   | NT                        | •               | CRT                         | СН              | MEFA         |                         | EM-II                                  | 1      | EC           |  |  |

| Wednesday                    | PS-I                                                                                   | STLD                      | NT              | EM-II                       | LUNCH           | ECS/EM-I LAB |                         |                                        |        |              |  |  |

| Thursday                     | NT                                                                                     | EM-II*                    | PS-I            | STLD                        |                 | ECS/EM-I LAB |                         |                                        |        |              |  |  |

| Friday                       | EM-II                                                                                  | EC                        | STLD            | NT                          |                 | MEFA         | A EC                    |                                        |        | PS-I         |  |  |

| Saturday                     | STLD                                                                                   | PS-I                      | EC              | MEFA                        |                 |              |                         | GENDER SENS                            | SITIZA | TION         |  |  |

| No                           |                                                                                        | Subject(T/P)              |                 | Fact                        | ılty Name       |              | Mob                     | oile No                                | Perio  | ods/Week     |  |  |

| 1                            | Netwo                                                                                  | ork Theory (A4            | 10213)          | Dr.S                        | S.Radhika       |              |                         |                                        |        | 4+1*-Periods |  |  |

| 2                            | Switching                                                                              | Theory and Lo<br>(A40407) | ogic Design     | Mrs.                        | D.Radhika       |              |                         |                                        |        | 4+1*-Periods |  |  |

| 3                            | Electrica                                                                              | al Machines-II            | (A40212)        | Mr.G.Srikanth/Mrs.D.Radhika |                 |              |                         |                                        |        | 4+1*-Periods |  |  |

| 4                            | Power                                                                                  | r Systems-I (A            | 10214)          | Mr.N.Santhinath             |                 |              |                         |                                        |        | 4+1*-Periods |  |  |

| 5                            | Manegerial                                                                             | Eeconomics a              | nd Financial    | Mrs.B                       | .P.S.Jyothi     | i            |                         |                                        |        | 4-Periods    |  |  |

|    | Analysis (A40010)                               |                                            |                 |

|----|-------------------------------------------------|--------------------------------------------|-----------------|

| 6  | Electronic Circuits (A40413)                    | Mrs.B.Mamatha                              | 4+1*-Periods    |

| 7  | GENDER SENSITIZATION                            | Mr.N.V.Bharadwaj                           | 3-Periods       |

| 8  | Electrical Machines-I LAB (A40287)              | Santhinath/Rakesh/Srikanth/NV<br>Bharadwaj | 3+3-Periods     |

| 9  | Electrical Circuits and Simulation LAB (A40286) | D.Krishna/D.Radhika/Dr.S.Radhika           | 3+3-<br>Periods |

| 10 | CACHE/LIB                                       | RARY/SPORTS/MENTORING                      | PERIODS         |

| 11 | Campu                                           | s Recruitment Training                     | 2<br>Periods    |

|    | *- Tutorial                                     |                                            | <u>.</u>        |

| Date: 3/1 <u>2/2015</u> | Dept. Coord: | -          |

|-------------------------|--------------|------------|

| HOD:                    | Dean Acad:   | Principal: |

# 13. Lecture schedule with methodology being used / adopted

| SL.No. | Unit<br>No. | Total<br>No. of<br>Periods | Week<br>No. | Topic to be covered in One lecture                               | Regular/<br>Additional | Teaching aids<br>used<br>LCD/OHP/BB | Remarks |

|--------|-------------|----------------------------|-------------|------------------------------------------------------------------|------------------------|-------------------------------------|---------|

| 1      | I           |                            | WEEK 1      | Introduction to switching theory and logic design                | Regular                | BB                                  |         |

| 2      |             |                            |             | Number Systems                                                   | Regular                | BB                                  |         |

| 3      |             |                            | -           | Number base conversions                                          | Regular                | BB                                  |         |

| 4      |             |                            | -           | Complement of numbers                                            | Regular                | BB                                  |         |

|        |             |                            | -           | TUTORIAL                                                         |                        |                                     |         |

| 5      |             |                            |             | Binary Codes, Binary<br>Coded Decimal Code and its<br>properties | Regular                | BB                                  |         |

| 6      |             |                            | WEEK 2      | Unit Distance Codes, Alpha<br>Numeric Codes                      | Regular                | BB                                  |         |

| 7      |             |                            |             | Error Detecting & correcting codes                               | Regular                | BB                                  |         |

| 8      |             |                            | -           | Tutorial class                                                   | Regular                | BB                                  |         |

| 8      |             |                            | -           | Fundamental & postulates of Boolean algebra                      | Regular                | BB                                  |         |

| 9      |             |                            | -           | Theorems and properties                                          | Regular                | BB                                  |         |

| 10     |             |                            | WEEK 3      | Switching functions                                              | Regular                | BB                                  |         |

| 11 |    |        | Canonical & standard forms                                           | Regular    | BB |

|----|----|--------|----------------------------------------------------------------------|------------|----|

|    |    |        | TUTORIAL                                                             |            |    |

| 12 |    |        | Algebraic simplification of digital logic gates                      | Regular    | BB |

| 13 |    |        | Inhibit circuits                                                     | Additional | BB |

| 16 |    |        | Properties of XOR Gates,<br>Universal Gates                          |            | BB |

| 17 |    | WEEK 4 | Multi-level NAND/NOR<br>Realizations                                 | Regular    | BB |

| 18 | II |        | Minimization with theorems                                           | Regular    | BB |

|    |    |        | TUTORIAL                                                             |            |    |

| 19 |    |        | k-Map Method                                                         | Regular    | BB |

| 20 |    |        | Five and Six variable Maps                                           | Regular    | BB |

| 21 |    |        | Prime and Essential Prime<br>Implications, Don't Care<br>Map Entries | Regular    | BB |

| 22 |    | WEEK 5 | Tabular Method                                                       | Regular    | BB |

|    |    |        | TUTORIAL                                                             |            |    |

| 23 |    |        | Partially Specified<br>Expressions                                   | Regular    | BB |

| 24 |    |        | Multi-output Minimization                                            | Regular    | BB |

| 25 |    |        | Combinational Design:<br>Arithmetic Circuits                         | Regular    | BB |

| 26 |    |        | Comparator                                                           | Regular    | ВВ |

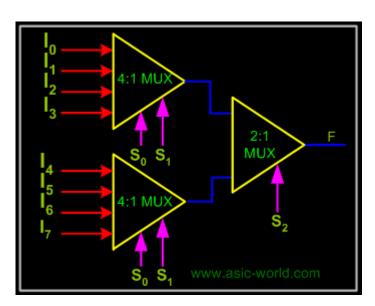

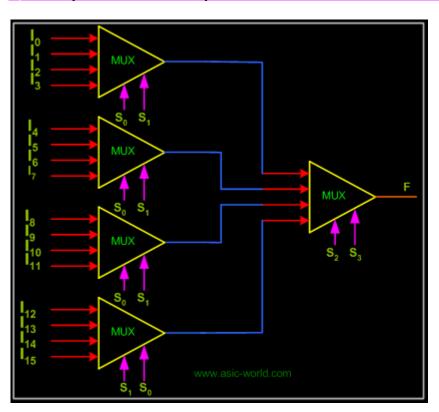

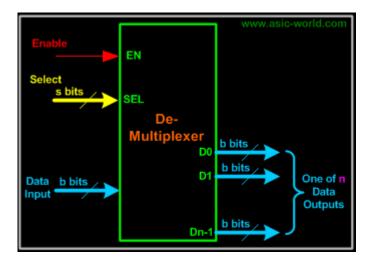

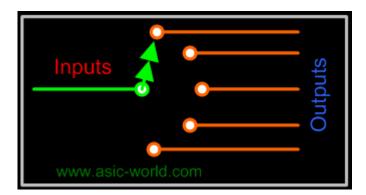

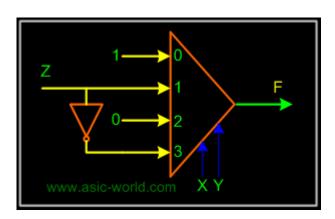

| 27 |    | WEEK 6 | Multiplexers                                                         | Regular    | BB |

| 28 |    |        | Code Converters                                                      | Regular    | BB |

|    |    |        | TUTORIAL                                                             |            |    |

| 29 |    |        | Wired Logic, Tri-state Bus<br>Systems                                | Additional | BB |

| 30 |    |        | Practical Aspects related to combinational Logic design              | Regular    | BB |

| 31 |     |   |         | TUTORIAL                                                                       | Regular    | BB |

|----|-----|---|---------|--------------------------------------------------------------------------------|------------|----|

| 32 | III |   | WEEK 7  | Sequential Machine<br>Fundamentals - introduction                              | Regular    | BB |

| 33 |     |   |         | Basic architectural distinctions between combinational and sequential circuits | Regular    | BB |

| 34 |     |   |         | Binary Cell, fundamentals of sequential machine operation                      | Regular    | BB |

| 35 |     |   |         | Flip-flop and types of flip-flops                                              | Regular    | BB |

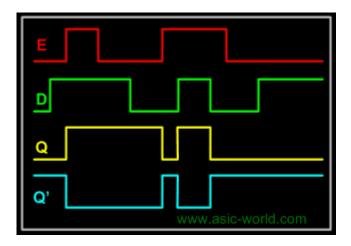

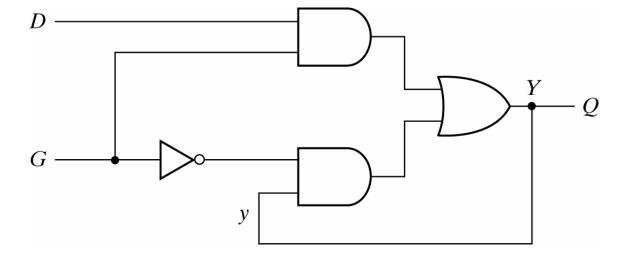

| 36 |     |   |         | D- Latch Flip-flop                                                             | Regular    | BB |

| 37 |     |   | WEEK 8  | Tutorials                                                                      | Regular    | BB |

| 38 |     |   |         |                                                                                | Regular    | BB |

| 39 |     |   |         |                                                                                |            | BB |

| 40 | VI  | 9 |         |                                                                                |            |    |

| 41 |     |   |         |                                                                                | Regular    | BB |

| 42 |     |   | WEEK 9  |                                                                                | Regular    | BB |

| 43 |     |   |         |                                                                                | Regular    | BB |

| 44 |     |   |         |                                                                                | Regular    | BB |

| 45 |     |   |         |                                                                                | Additional | BB |

| 46 |     |   |         |                                                                                |            | BB |

| 47 |     |   |         | B.TECH I-MID<br>INTERNAL<br>EXAMINATIONS                                       |            |    |

| 48 |     |   | WEEK 10 |                                                                                |            |    |

| 49 | v   |   |         |                                                                                | Regular    | BB |

| 50 |     |   |         |                                                                                | Regular    | BB |

| 51 |     |   |         |                                                                                | Regular    | BB |

| 52 |     |   |         |                                                                                | Regular    | BB |

| 53 | WEEK 11<br>(15 <sup>TH</sup> SEP | Regular    | BB |

|----|----------------------------------|------------|----|

| 54 | TO 21 <sup>ST</sup><br>SEP)      |            | BB |

| 55 |                                  |            |    |

| 56 |                                  | Regular    | BB |

| 57 |                                  | Regular    | BB |

| 58 | WEEK 12                          | Regular    | BB |

| 59 |                                  | Regular    | BB |

| 60 |                                  | Additional | BB |

| 61 |                                  |            | BB |

| 62 |                                  |            | BB |

| 63 |                                  |            |    |

## 14. Detailed Notes

## **Digital and Analog Signals**

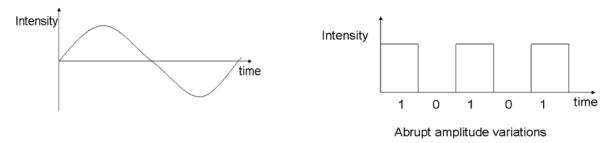

Signals carry information and are defined as any physical quantity that varies with time, space, or any other independent variable. For example, a sine wave whose amplitude varies with respect to time or the motion of a particle with respect to space can be considered as signals. A system can be defined as a physical device that performs an operation on a signal. For example, an amplifier is used to amplify the input signal amplitude. In this case, the amplifier performs some operation(s) on the signal, which has the effect of increasing the amplitude of the desired information-bearing signal.

Signals can be categorized in various ways; for example discrete and continuous time domains. Discrete-time signals are defined only on a discrete set of times. Continuous-time signals are often referred to as continuous signals even when the signal functions are not continuous; an example is a square-wave signal.

Figure 1a: Analog Signal

Figure 1b: Digital Signal

Another category of signals is discrete-valued and continuous-valued or otherwise known as digital and analog signals. Digital signals are discrete-valued and analog signals are continuous electrical signals that vary in time as shown in Figure 1 (a) and (b). Analog devices and systems process signals whose voltages or other quantities vary in a continuous manner.

They can take on any value across a continuous range of voltage, current, or other metric. The analog signals can have an infinite number of values. Analog systems can be called wave systems. They have a value that changes steadily over time and can have any one of an infinite set of values in a range. Analog signals represent some physical quantity and they can be a model of the real quantity. Most of the time, the variations corresponds to that of the non-electric (original) signal. For example, the telephone transmitter converts the sounds into an electrical voltage signal. The intensity of the voice causes electric current variations. Therefore, the two are analogous hence the name analog. At the receiving end, the signal is reproduced in the same proportion. Hence the electric current is a model and is an electrical representation of one's voice.

Not all analog signals vary as smoothly as the waveform shown in Fig 1(a). Digital signals are non-continuous, they change in individual steps. They consist of pulses or digits with discrete levels or values. The value of each pulse is constant, but there is an abrupt change from one digit to the next. Digital signals have two amplitude levels. The value of which are specified as one of two possibilities such as 1 or 0, HIGH or LOW, TRUE or FALSE and so on. In reality, the values are anywhere within specific ranges and we define values within a given range.

A digital system is the one that handles only discrete values or signals. Any set that is restricted to a finite number of elements contains discrete information. The word digital describes any system based on discontinuous data or events. Digital is the method of storing, processing and transmitting information through the use of distinct electronic pulses that represent the binary digits 0 and 1. Examples of discrete sets are the 10 decimal digits, the 26 letters of the alphabet etc. A digital system would be to flick the light switch on and off. There's no 'in between' values.

#### Advantages of digital signals

The usual advantages of digital circuits when compared to analog circuits are:

**Noise Margin** (**resistance to noise/robustness**): Digital circuits are less affected by noise. If the noise is below a certain level (the noise margin), a digital circuit behaves as if there was no noise at all. The stream of bits can be reconstructed into a perfect replica of the original source. However, if the noise exceeds this level, the digital circuit cannot give correct results.

**Error Correction and Detection**: Digital signals can be regenerated to achieve lossless data transmission, within certain limits. Analog signal transmission and processing, by contrast, always introduces noise.

**Easily Programmable**: Digital systems interface well with computers and are easy to control with software. It is often possible to add new features to a digital system without changing hardware, and to do this remotely, just by uploading new software. Design errors or bugs can be worked-around with a software upgrade, after the product is in customer hands. A digital system is often preferred because of (re-)programmability and ease of upgrading without requiring hardware changes.

Cheap Electronic Circuits: More digital circuitry can be fabricated per square millimeter of integrated-circuit material. Information storage can be much easier in digital systems than in analog ones. In particular, the great noise-immunity of digital systems makes it possible to store data and retrieve it later without degradation. In an analog system, aging and wear and tear will degrade the information in storage, but in a digital system, as long as the wear and tear is below a certain level, the information can be recovered perfectly. Theoretically, there is no data-loss when copying digital data. This is a great advantage over analog systems, which faithfully reproduce every bit of noise that makes its way into the signal.

Disadvantages The world in which we live is analog, and signals from this world such as light, temperature, sound, electrical conductivity, electric and magnetic fields, and phenomena such as the flow of time, are for most practical purposes continuous and thus analog quantities rather than discrete digital ones. For a digital system to do useful things in the real world, translation from the continuous realm to the discrete digital realm must occur, resulting in quantization errors. This problem can usually be mitigated by designing the system to store enough digital data to represent the signal to the desired degree of fidelity. The Nyquist-Shannon sampling theorem provides an important guideline as to how much digital data is needed to accurately portray a given analog signal.

Digital systems can be fragile, in that if a single piece of digital data is lost or misinterpreted, the meaning of large blocks of related data can completely change. This problem can be diminished by designing the digital system for robustness. For example, a parity bit or other error-detecting or error-correcting code can be inserted into the signal path so that minor data corruptions can be detected and possibly corrected.

Digital circuits use more energy than analog circuits to accomplish the same calculations and signal processing tasks, thus producing more heat as well. In portable or battery-powered systems this can be a major limiting factor.

Digital circuits are made from analog components, and care has to be taken to all noise and timing margins, to parasitic inductances and capacitances, to proper filtering of power and ground connections, to electromagnetic coupling amongst data lines. Inattention to these can cause problems such as "glitches", pulses do not reach valid switching (threshold) voltages, or unexpected ("undecoded") combinations of logic states.

A corollary of the fact that digital circuits are made from analog components is the fact that digital circuits are slower to perform calculations than analog circuits that occupy a similar amount of physical space and consume the same amount of power. However, the digital circuit will perform the calculation with much better repeatability, due to the high noise immunity of digital circuitry.

#### Introduction

Number systems provide the basis for all operations in information processing systems. In a number system the information is divided into a group of symbols; for example, 26 English letters, 10 decimal digits etc. In conventional arithmetic, a number system based upon ten units (0 to 9) is used. However, arithmetic and logic circuits used in computers and other digital systems operate with only 0's and 1's because it is very difficult to design circuits that require ten distinct states. The number system with the basic symbols 0 and 1 is called binary. ie. A binary system uses just two discrete values. The binary digit (either 0 or 1) is called a bit.

A group of bits which is used to represent the discrete elements of information is a symbol. The mapping of symbols to a binary value is known a binary code. This mapping must be unique. For example, the decimal digits 0 through 9 are represented in a digital system with a code of four bits. Thus a digital system is a system that manipulates discrete elements of information that is represented internally in binary form.

#### **Decimal Numbers**

The invention of decimal number system has been the most important factor in the development of science and technology. The decimal number system uses positional number representation, which means that the value of each digit is determined by its position in a number.

The base, also called the radix of a number system is the number of symbols that the system contains. The decimal system has ten symbols: 0,1,2,3,4,5,6,7,8,9. In other words, it has a base of 10. Each position in the decimal system is 10 times more significant than the previous position. The numeric value of a decimal number is determined by multiplying each digit of the number by the value of the position in which the digit appears and then adding the products. Thus the number 2734 is interpreted as

$$2 \times 1000 + 7 \times 100 + 3 \times 10 + 4 \times 1 = 2000 + 700 + 30 + 4$$

Here 4 is the least significant digit (LSD) and 2 is the most significant digit (MSD).

In general in a number system with a base or radix r, the digits used are from 0 to r-1 and the number can be represented as

$$N = a_n r^n + a_{n-1} r^{n-1} + \dots + a_1 r^1 + a_0 r^0$$

where, for  $n = 0, 1, 2, 3, \dots (1)$

$r = \text{base or radix of the system.}$

$a = \text{number of digits having values between 0 and r-1}$

Equation (1) is for all integers and for the fractions (numbers between 0 and 1), the following equation holds.

$$N = a_{-1}r^{-1} + a_{-2}r^{-2} + \dots + a_{-m+1}r^{-m+1} + a_{-m}r^{m}$$

Thus for decimal fraction 0.7123

$$N = 0.7000 + 0.0100 + 0.0020 + 0.0003$$

where

$$a - 1 = 7$$

$a - 2 = 1$

$a - 3 = 2$

$a - 4 = 3$

#### **Binary Numbers**

The binary number has a radix of 2. As r = 2, only two digits are needed, and these are 0 and 1. Like the decimal system, binary is a positional system, except that each bit position corresponds to a power of 2 instead of a power of 10. In digital systems, the binary number system and other number systems closely related to it are used almost exclusively. Hence, digital systems often provide conversion between decimal and binary numbers. The decimal value of a binary number can be formed by multiplying each power of 2 by either 1 or 0 followed by adding the values together.

**Example:** The decimal equivalent of the binary number 101010.

$$= 1 \times 25 + 0 \times 24 + 1 \times 23 + 0 \times 22 + 1 \times 21 + 0 \times 20$$

$$= 43$$

In binary r bits can represent  $n = 2^r$  symbols. e.g. 3 bits can represent up to 8 symbols, 4 bits for 16 symbols etc. For N symbols to be represented, the minimum number of bits required is the lowest integer 'r' that satisfies the relationship.

$$2^r > N$$

e.g. if  $N = 26$ , minimum r is 5 since  $2^4 = 16$  and  $2^5 = 32$ .

#### **Octal Numbers**

Digital systems operate only on binary numbers. Since binary numbers are often very long, two shorthand notations, octal and hexadecimal, are used for representing large binary numbers. Octal systems use a base or radix of 8. Thus it has digits

from 0 to 7 (r-1). As in the decimal and binary systems, the positional valued of each digit in a sequence of numbers is

fixed. Each position in an octal number is a power of 8, and each position is 8 times more significant than the previous position.

**Example:** The decimal equivalent of the octal number 15.2.

$$N = 15.2_{8}$$

$$= 1 \times 8^{1} + 5 \times 8^{0} + 2 \times 8^{1}$$

$$= 13.25$$

#### **Hexadecimal Numbers**

The hexadecimal numbering system has a base of 16. There are 16 symbols. The decimal digits 0 to 9 are used as the first ten digits as in the decimal system, followed by the letters A, B, C, D, E and F, which represent the values 10, 11,12,13,14 and 15 respectively. Table 1 shows the relationship between decimal, binary, octal and hexadecimal number systems.

| Decimal | Binary | Octal | Hexadecimal |

|---------|--------|-------|-------------|

| 0       | 0000   | 0     | 0           |

| 1       | 0001   | 1     | 1           |

| 2       | 0010   | 2     | 2           |

| 3       | 0011   | 3     | 3           |

| 4       | 0100   | 4     | 4           |

| 5       | 0101   | 5     | 5           |

| 6       | 0110   | 6     | 6           |

| 7       | 0111   | 7     | 7           |

| 8       | 1000   | 10    | 8           |

| 9       | 1001   | 11    | 9           |

| 10      | 1010   | 12    | A           |

| 11      | 1011   | 13    | В           |

| 12      | 1100   | 14    | C           |

| 13      | 1101   | 15    | D           |

| 14      | 1110   | 16    | Е           |

| 15      | 1111   | 17    | F           |

Hexadecimal numbers are often used in describing the data in computer memory. A computer memory stores a large number of words, each of which is a standard size collection of bits. An 8-bit word is known as a **Byte.** A hexadecimal digit may be considered as half of a byte. Two hexadecimal digits constitute one byte, the rightmost 4 bits corresponding to half a byte, and the leftmost 4 bits corresponding to the other half of the byte. Often a half-byte is called nibble.

If "word" size is n bits there are 2n possible bit patterns so only 2n possible distinct numbers can be represented. It implies that all possible numbers cannot be represent and some of these bit patterns (half?) to represent negative numbers. The negative numbers are generally represented with sign magnitude i.e. reserve one bit for the sign and the rest of bits are interpreted directly as the number. For example in a 4 bit system, 0000 to 0111 can be used to positive numbers from +0 to  $+2^{n-1}$  and represent 1000 to 1111 can be used for negative numbers from +0 to  $+2^{n-1}$ . The two possible zero's redundant and also it can be seen that such representations are arithmetically costly.

Another way to represent negative numbers are by radix and radix-1 complement (also called r's and (r-1)'s). For example -k is represented as  $\mathbb{R}^n$  -k. In the case of base 10 and corresponding 10's complement with n=2, 0 to 99 are the possible numbers. In such a system, 0 to 49 is reserved for positive numbers and 50 to 99 are for positive numbers.

Examples:

$$+3 = 43$$

$+3 = 43$

## **Example:**

$119\ 10 = 01110111\ 2$

Complementing bits will result

#### **Properties of Two's Complement Numbers**

- 1. X plus the complement of X equals 0.

- 2. There is one unique 0.

- 3. Positive numbers have 0 as their leading bit (MSB); while negatives have 1 as their MSB.

- 4. The range for an n-bit binary number in 2's complement representation is from -2 (n-1) to 2 (n-1) 1

- 5. The complement of the complement of a number is the original number.

- 6. Subtraction is done by addition to the 2's complement of the number.

Value of Two's Complement Numbers

For an n-bit 2's complement number the weights of the bits is the same as for unsigned numbers except of the MSB. For the MSB or sign bit, the weight is  $-2^{n-1}$ . The value of the n-bit 2's complement number is given by:

A

$$_{2\text{'s-complement}} = (a^{n-1}) \times (-2^{n-1}) + (a^{n-2}) \times (2^{n-1}) + ... (a_1) \times (2^1) + a_0$$

For example, the value of the 4-bit 2's complement number 1011 is given by:

```

= 1 x -2^{3} + 0 x 2^{2} + 1 x 2^{1} + 1

= -8 + 0 + 2 + 1

= -5

```

An n-bit 2's complement number can converted to an m-bit number where m>n by appending m-n copies of the sign bit to the left of the number. This process is called sign extension. Example: To convert the 4-bit 2's complement number 1011 to an 8-bit representation, the sign bit (here = 1) must be extended by appending four 1's to left of the number:

To verify that the value of the 8-bit number is still -5; value of 8-bit number

```

= -27 + 26 + 25 + 24 + 23 +2 +1

= -128 + 64 + 32 + 16 +8 +2+1

= -128 + 123 = -5

```

Similar to decimal number addition, two binary numbers are added by adding each pair of bits together with carry propagation. An addition example is illustrated below:

```

Y 141

X + Y 331

1011111000 Carry

101111110 X

+10001101 Y

```

190

X

Similar to addition, two binary numbers are subtracted by subtracting each pair of bits together with borrowing, where needed. For example:

```

X 229

Y 46

X - Y 183

0 0 1 1 1 1 1 1 0 0 Borrow

1 1 1 0 0 1 0 1 X

0 0 1 0 1 1 1 1 0 Y

1 0 1 1 0 1 1 1 1 X - Y

```

Two' complement addition/subtraction example

```

4 0100 -2 1110

-7 1001 -6 1010

-3 1101 -8 11000

```

Overflow occurs if signs (MSBs) of both operands are the same and the sign of the result is different. Overflow can also be detected if the carry in the sign position is different from the carry out of the sign position. Ignore carry out from MSB.

#### **Number Base Conversions**

This section describes the conversion of numbers from one number system to another. Radix Divide and Multiply Method is generally used for conversion. There is a general procedure for the operation of converting a decimal number to a

number in base r. If the number includes a radix point, it is necessary to separate the number into an integer part and a fraction part, since each part must be converted differently. The conversion of a decimal integer to a number in base r is done by dividing the number and all successive quotients by r and accumulating the remainders. The conversion of a decimal fraction is done by repeated multiplication by r and the integers are accumulated instead of remainders.

Integer part - repeated divisions by r yield LSD to MSD

Fractional part - repeated multiplications by r yield MSD to LSD

**Example:** Conversion of decimal 23 to binary is by divide decimal value by 2 (the base) until the value is 0

```

Integer remainder

23

11 1 → LSB

5 1 ↑

2 1 1

1 0

0 1 → MSE

```

The answer is 23  $_{10} = 10111 _{2}$

Divide number by 2; keep track of remainder; repeat with dividend equal to quotient until zero; first remainder is binary LSB and last is MSB.

The conversion from decimal integers to any base-r system is similar to this above example, except that division is done by r instead of 2.

#### **Example:**

Convert (0.7854) 10 to binary.

```

0.7854 \times 2 = 1.5708; a _{-1} = 1

0.5708 \times 2 = 1.1416; a _{-2} = 1

0.1416 \times 2 = 0.2832; a _{-3} = 0

0.2832 \times 2 = 0.5664; a _{-4} = 0

The answer is (0.7854)_{-10} = (0.1100)_{-2}

```

Multiply fraction by two; keep track of integer part; repeat with multiplier equal to product fraction; first integer is MSB, last is the LSB; conversion may not be exact; a repeated fraction. The conversion from decimal fraction to any base-r system is similar to this above example, except the multiplication is done by r instead of 2.

The conversion of decimal numbers with both integer and fraction parts is done by converting the integer and the fraction separately and then combining the two answers.

Thus

$$(23.7854)_{10} = (10111.1100)_2$$

For converting a binary number to octal, the following two step procedure can be used.

- 1. Group the number of bits into 3's starting at least significant symbol. If the number of bits is not evenly divisible by 3, then add 0's at the most significant end.

- 2. Write the corresponding 1 octal digit for each group

#### **Examples:**

Similarly for converting a binary number to hex, the following two step procedure can be used.

- 1. Group the number of bits into 4's starting at least significant symbol. If the number of bits is not evenly divisible by 4, then add 0's at the most significant end.

- 2. Write the corresponding 1 hex digit for each group

#### **Examples:**

```

1001 1110 0111 0000 (binary)

9 e 7 0 (hex)

1 1111 1010 0011 (binary)

1 f a 3 (hex)

```

The hex to binary conversion is very simple; just write down the 4 bit binary code for each hexadecimal digit

#### **Example:**

Similarly for octal to binary conversion, write down the 8 bit binary code for each octal digit.

The hex to octal conversion can be carried out in 2 steps; first the hex to binary followed by the binary to octal. Similarly, decimal to hex conversion is completed in 2 steps; first the decimal to binary and from binary to hex as described above.

#### **Boolean Algebra and Basic Operators**

Due to historical reasons, digital circuits are called switching circuits, digital circuit functions are called switching functions and the algebra is called switching algebra. The algebraic system known as Boolean algebra named after the mathematician George Boole. George Boole Invented multi-valued discrete algebra (1854) and E. V. Huntington developed its postulates and theorems (1904). Historically, the theory of switching networks (or systems) is credited to Claude Shannon, who applied mathematical logic to describe relay circuits (1938). Relays are controlled electromechanical switches and they have been replaced by electronic controlled switches called logic gates. A special case of Boolean Algebra known as Switching Algebra is a useful mathematical model for describing the combinational circuits. In this section we will briefly discus how the Boolean algebra is applied to the design of digital systems. Examples of Huntington 's postulates are given below:

#### Closure

If X and Y are in set (0, 1) then operations  $X^{+\gamma}$  and  $X^{-\gamma}$  are also in set (0, 1)

#### **Identity**

$$X + 0 = X$$

$X \cdot 1 = X$

#### Distributive

$$X \cdot (Y + Z) = (X \cdot Y) + (X \cdot Z)$$

$$X + (Y \cdot Z) = (X + Y) \cdot (X + Z)$$

## Complement

$$X + \overline{X} = 1$$

$$X \cdot \underline{X} = 0$$

Note that for each property, one form is the dual of the other; (zeros to ones, ones to zeros, '.' operations to '+' operations, '+' operations to '.' operations).

From the above postulates the following theorems could be derived.

#### **Associative**

$$X + (Y + Z) = (X + Y) + Z$$

$$X \cdot (Y \cdot Z) = (X \cdot Y) \cdot Z$$

#### Idempotence

$$X \cdot X = X$$

$$X + X = X$$

#### Absorption

$$X + (X \cdot Y) = X$$

$X \cdot (X + Y) = X$

#### Simplification

$$X \cdot (\underline{X} + \lambda) = X \cdot \lambda$$

$X \cdot (\underline{X} + \lambda) = X \cdot \lambda$

#### Consensus

#### Adjacency

$$X \cdot Y + X \cdot \overline{Y} = X$$

$(X + Y) \cdot (X + \overline{Y}) = X$

#### **Demorgans**

$$\frac{\overline{X} + \overline{Y}}{\overline{X} \cdot \overline{Y}} = \frac{\overline{X}}{\overline{X}} \cdot \frac{\overline{Y}}{\overline{Y}}$$

In general form

$$\overline{F(\cdot, +, X_1, \dots X_n)} = G(+, \cdot, \overline{X_1}, \dots \overline{X_n})$$

Very useful for complementing function expressions; for example

$$\begin{array}{ll} F = X + Y \cdot Z; & \overline{F} = \overline{X + Y \cdot Z} \\ \overline{F} = \overline{X} \cdot \overline{Y \cdot Z} & F = \overline{X} \cdot \left(\overline{Y} + \overline{Z}\right) \\ \overline{F} = \overline{X} \cdot \overline{Y} + \overline{X} \cdot \overline{Z} \end{array}$$

## **Switching Algebra Operations**

A set is a collection of objects (or elements) and for example a set Z {0, 1} means that Z is a set containing two elements distinguished by the symbols 0 and 1. There are three primary operations AND , OR and NOT.

#### **NOT**

It is anary complement or inversion operation. Usually shown as over bar (  $\overline{\mathbb{X}}$  ), other forms are  $\mathbb{X}'$  and  $\sim\!\!\mathbb{X}$

#### **AND**

Also known as the conjunction operation; output is true (1) only if all inputs are true. Algebraic operators are '.', '&', ' ^ '

#### OR

Also known as the disjunction operation; output is true (1) if any input is true. Algebraic operators are '+', '|', ' \subset '

AND and OR are called binary operations because they are defined on two operands X and Y. Not is called a unary operation because it is defined on a single operand X. All of these operations are closed. That means if one applies the operation to two elements in a set  $Z \{0, 1\}$ , the result will be always an element in the set B and not something else.

Like standard algebra, switching algebra operators have a precedence of evaluation. The following rules are useful in this regard.

- 1. NOT operations have the highest precedence

- 2. AND operations are next

- 3. OR operations are lowest

- 4. Parentheses explicitly define the order of operator evaluation and it is a good practice to use parentheses especially for situations which can cases doubt.

Note that in Boolean algebra the operators AND and OR are not linear group operations; so one cannot solve equations by "adding to" of "multiplying" on both sides of the equal sign as is done with real, complex numbers in standard algebra.

#### 1.1 Introduction

Number system is a basis for counting various items. On hearing the word 'number', all of us immediately think of the familiar decimal number system with its 10 digits: 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9.

Modern computers communicate and operate with binary numbers which use only the digits 0 and 1. Let us consider decimal number 18. This number is represented in binary as 10010. In the example, if decimal number is considered, we require only two digits to represent the number, whereas if binary number is considered we require five digits. Therefore we can say that, when decimal quantities are represented in the binary form, they take more digits. For large decimal numbers people have to deal with very large binary strings and therefore, they do not like working with binary numbers. This fact gave rise to three new number systems: Octal, Hexadecimal and Binary Coded Decimal (BCD). These number systems represent binary number in a compressed form. Therefore, these number systems are now widely used to compress long strings of binary numbers.

In this chapter, we discuss binary, octal, hexadecimal, and BCD number systems, and we will see how to convert from decimal to binary, octal and hexadecimal, and vice versa. In the later section of this chapter we are going to see binary, hexadecimal, Excess-3 and BCD arithmetic.

## 1.2 Decimal Number System

Before considering any number system, let us consider familiar decimal number system. In decimal number system we can express any decimal number in units, tens, hundreds, thousands and so on. When we write a decimal number say, 5678.9, we know it can be represented as

$$5000 + 600 + 70 + 8 + 0.9 = 5678.9$$

## Binary Number System

We know that decimal system with its ten digits is a base-ten system. Similarly, binary system with its two digits is a base-two system. The two binary digits (bits) are 1 and 0. Like digital system, in binary system each binary digit commonly known as bit, has its own value or weight.

## Octal Number System

We know that the base of the decimal number system is 10 because it uses the digits 0 to 9, and the base of binary number system is 2 because it uses digits 0 and 1. The octal number system uses first eight digits of decimal number system: 0, 1, 2, 3, 4, 5, 6, and 7. As it uses 8 digits, its base is 8.

## **Hexadecimal Number System**

The hexadecimal number system has a base of 16 having 16 digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E and F. It is another number system that is particularly useful for human communications with a computer. Although it is somewhat more difficult to interpret than the octal number system, it has become the most popular. Since its base is a power of 2 (24), it is easy to convert hexadecimal numbers to binary and vice versa.

## Converting any Radix to Decimal

In general, numbers can be represented as

$$N = A_{n-1} r^{n-1} + A_{n-2} r^{n-2} + ... + A_i r^i + A_0 r^0$$

+  $A_{-1} r^{-1} + A_{-2} r^{-2} + ... C_{-m} r^{-m}$

where N = Number in decimal

A = Digit

r = Radix or base of a number system

n = The number of digits in the integer portion of number

m = The number of digits in the fractional

portion of number

From this general equation we can convert number with any radix into its decimal equivalent.

## Conversion of Decimal Numbers to any Radix Number

We have to carry out the conversion of decimal number to any radix number in two steps. In step 1, we have to convert integer part and in step 2 we have to convert fractional part. The conversion of integer part is accomplished by successive division method, and the conversion of fractional part is accomplished by successive multiplication method.

## Successive Division for Integer Part Conversion

In this method we repeatedly divide the integer part of the decimal number by r (the new radix) until quotient is zero. The remainder of each division becomes the numeral in the new radix. The remainders are taken in the reverse order to form a new radix number. This means that the first remainder is the least significant digit (LSD) and the last remainder is the most significant digit (MSD) in the new radix number.

## Successive Multiplication for Fractional Part Conversion

Conversion of fractional decimal numbers to another radix number is accomplished using a successive multiplication method. In this method, the number to be converted is multiplied by the radix of the new number, producing a product that has an integer part and a fractional part. The integer part (carry) of the product becomes a numeral in the new radix number. The fractional part is again multiplied by the radix and this process is repeated until fractional part reaches 0 or until the new radix number is carried out to sufficient digits. The integer part (carry) of each product is read downward to represent the new radix number.

## Complement Representation of Negative Numbers

In digital computers, to simplify the subtraction operation and for logical manipulation complements are used. There are two types of complements for each radix system: The radix complement and diminished radix complement. The first is referred to as the r's complement and the second as the (r-1)'s complement. For example, in binary system we substitute base value 2 in place of r to refer complements as 2's complement and 1's complement. In decimal number system, we substitute base value 10 in place of r to refer complements as 10's complement and 9's complement.

## 1's Complement Representation

The 1's complement of a binary number is the number that results when we change all 1's to zeros and the zeros to ones.

## 2's Complement Representation

The 2's complement is the binary number that results when we add 1 to the 1's complement. It is given as

2's complement = 1's complement + 1

The 2's complement form is used to represent negative numbers.

#### Rules for Binary Addition

| Α |   | В | SUM | CARRY |

|---|---|---|-----|-------|

| 0 | + | 0 | 0   | 0     |

| 0 | + | 1 | 1   | 0     |

| 1 | + | 0 | 1   | 0     |

| 1 | + | 1 | 0   | 1     |

Rules for Binary subtraction

| Α   | В   | Diff. | Borrow |

|-----|-----|-------|--------|

| 0 - | - 0 | 0     | 0      |

| 0 - | - 1 | 1     | . 1    |

| 1 . | - 0 | 1     | 0 .    |

| 1 - | - 1 | 0     | 0      |

## Classification of Binary Codes

#### Excess-3 Code

Excess-3 code is a modified form of a BCD number. The Excess-3 code can be derived from the natural BCD code by adding 3 to each coded number. For example, decimal 12 can be represented in BCD as 0001 0010. Now adding 3 to each digit we get Excess-3 code as 0100 0101 (12 in decimal).

Table shows excess-3 codes to represent single decimal digit

| Decimal digit | E | xcess | -3 Co | ie |

|---------------|---|-------|-------|----|

| 0             | 0 | 0     | 1     | 1  |

| 1             | 0 | 1     | 0     | 0  |

| 2             | 0 | 1     | 0     | 1  |

| 3             | 0 | 1     | 1     | 0  |

| 4             | 0 | 1     | 1     | 1  |

| 5             | 1 | 0     | 0     | 0  |

| 6             | 1 | 0     | 0     | 1  |

| 7             | 1 | 0     | 1     | 0  |

| 8             | 1 | 0     | 1     | 1  |

| 9             | 1 | 1     | 0     | 0  |

Excess-3 code

#### Excess-3 Addition

To perform Excess-3 addition we have to

- Add two Excess-3 numbers

- If Carry =  $1 \rightarrow \text{add } 3$  to the sum of two digits

- $= 0 \rightarrow \text{subtract } 3$

## **Excess-3 Subtraction**

To perform Excess-3 subtraction we have to

- Complement the subtrahend

- Add complemented subtrahend to minuend

- If carry = 1 Result is positive. Add 3 and end around carry

- If carry = 0 Result is negative. Subtract 3.

## **Gray Code**

Gray code is a special case of unit-distance code. In unit-distance code, bit patterns for two consecutive numbers differ in only one bit position. These codes are also called cyclic codes.

| Decimal<br>Code | Gray code |                                              |

|-----------------|-----------|----------------------------------------------|

| 0               | 0000      | <b>4</b>                                     |

| 1               | 0001      | ←                                            |

| 2               | 0011      | <b>│ ←</b>                                   |

| 3               | 0010      | <b>←</b>                                     |

| 4               | 0110      | <b>│ ◆────</b> ┐                             |

| 5               | 0111      | ←                                            |

| 6               | 0101      | <b>│ ←</b> ──┐                               |

| 7               | 0100      | <b>├</b> ─┐                                  |

| 8               | 1100      | <b>←</b>                                     |

| 9               | 1101      | ←                                            |

| 10              | 1111      | <b>│                                    </b> |

| 11              | 1110      | ←                                            |

| 12              | 1010      | ←                                            |

| 13              | 1011      | <b></b>                                      |

| 14              | 1001      | <b>→</b>                                     |

| 15              | 1000      | <b></b>                                      |

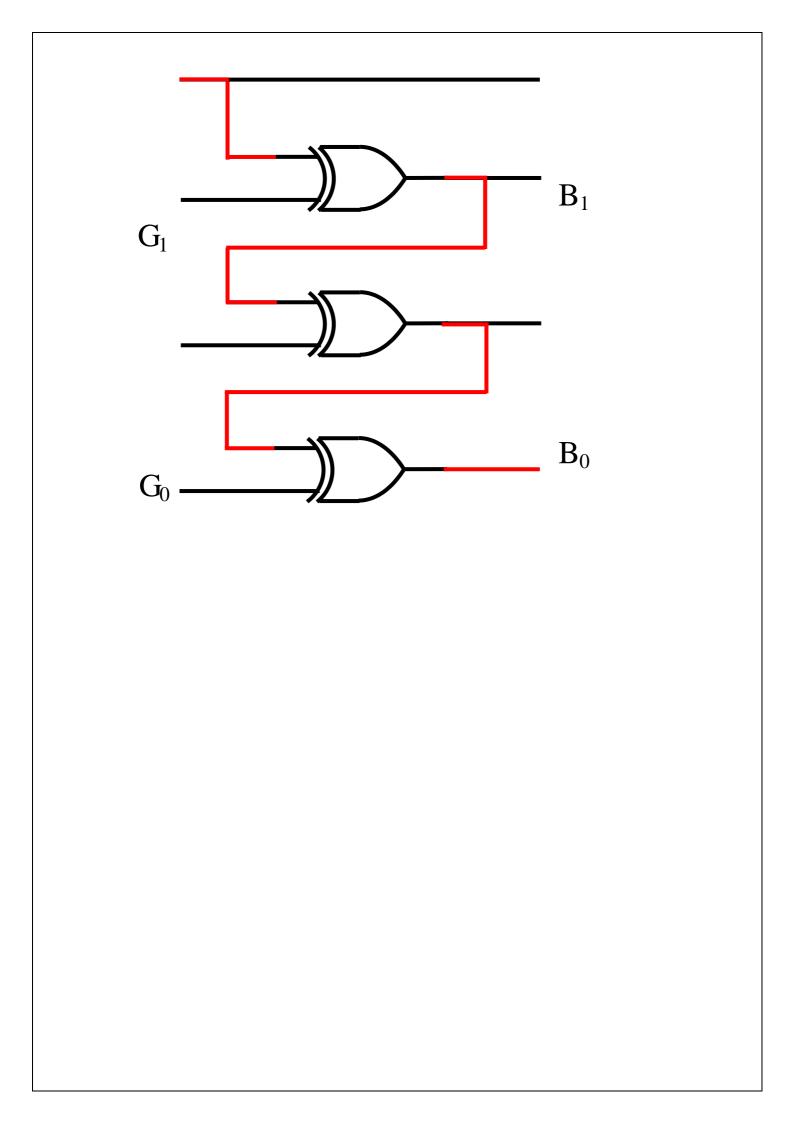

## Gray-to-Binary Conversion

The gray to binary code conversion can be achieved using following steps.

- The most significant bit of the binary number is the same as the most significant bit of the gray code number. So write it down.

- To obtain the next binary digit, perform an exclusive-OR-operation between the bit just written down and the next gray code bit. Write down the result.

- Repeat step 2 until all gray code bits have been exclusive-ORed with binary digits. The sequence of bits that have been written down is the binary equivalent of the gray-code number.

## Binary to Gray Conversion

Let us represent binary number as

$$B_1$$

$B_2$   $B_3$   $B_4$  ...  $B_n$  and its equivalent gray code as  $G_1$   $G_2$   $G_3$   $G_4$  ...  $G_n$ .

With this representation gray code bits are obtained from the binary bits follows:

$$G_1 = B_1$$

$G_2 = B_1 \oplus B_2$

$G_3 = B_2 \oplus B_3$

$G_4 = B_3 \oplus B_4$

:

:

:

:

:

:

:

:

:

## **Parity Bit**

A parity bit is used for the purpose of detecting errors during transmission of binary information. A parity bit is an extra bit included with a binary message to make the number of 1s either odd or even. The message, including the parity bit is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted. The circuit that generates the parity bit in the transmitter is called a parity generator and the circuit that checks the parity in the receiver is called a parity checker.

In even parity the added parity bit will make the total number of 1s an even amount. In odd parity the added parity bit will make the total number of 1s an odd amount.

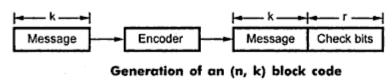

## **Linear Block Codes**

Block codes are not necessarily linear, but general all block codes used in practice are linear. A linear block code consists of k message bits and r check bits. These r check bits are derived from the original k message bits to form a n-bit block code, as shown in the Fig. The addition of the r check bits introduces redundancy into the code, thus enabling some form of error control. Such a code is designated as an (n, k) code. At the receiving end, the check bits are used to decide the validity of the received message.

## Matrix Representation of Linear Block Codes

In this method, matrices are used to encode the massage. Now before going to see generalized equations for matrix encoding we will see the illustration of matrix encoding with the help of example.

Let us assume that we have to transmit 2-bit binary codes. So we can only have four symbols in our word set. Let our message be :

Now we have to encode these messages by coding matrix. Coding matrix is also called the generation matrix. It has the form

$$G = [I_k : A]_{k \times n}$$

where

Ik is the identity matrix of order k and

A is an arbitrary  $k \times (n - k)$  sub-matrix.

When the arbitrary sub-matrix A has been specified, the (n, k) block code can be defined completely so that an important step in the design of an (n, k) block code is the structure of A. One of the important criterion in the choice of A is that the resulting code should allow the correction of a codeword received in error.

As an example of the construction of an (n, k) block code, consider the A sub-matrix (2, 2) as

$$A = \begin{bmatrix} 1 & 1 \\ 0 & 1 \end{bmatrix}$$

We know that generation matrix is given as